January 19, 2026 : India is making a focused push to strengthen its position in the global semiconductor value chain by investing heavily in chip design capabilities. At the centre of this effort is the Chips to Start-up (C2S) Programme, launched in 2022 by the Ministry of Electronics and Information Technology. With the global semiconductor market expected to approach USD 1 trillion by 2030 and a projected worldwide shortage of more than one million skilled professionals by 2032, India is using this window to build deep, indigenous expertise in a sector where it already has a strong design talent base.

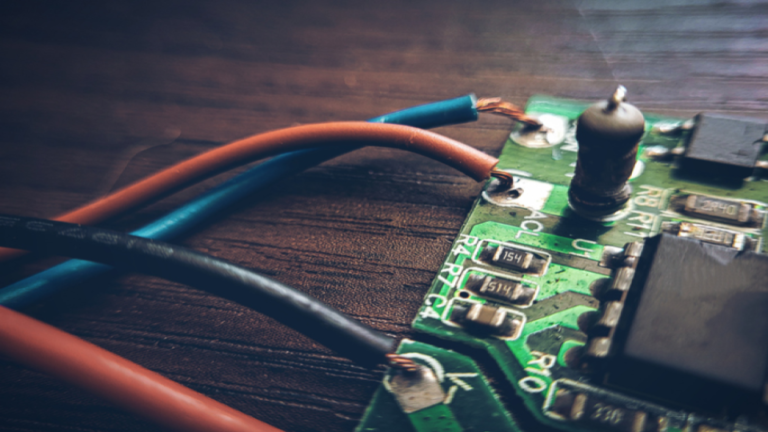

Semiconductors underpin almost every modern technology, from artificial intelligence and telecommunications to defence systems, automobiles, and consumer electronics. Although India has long been a global hub for chip design services, it has remained dependent on overseas foundries for fabrication. The C2S Programme addresses this gap by enabling students, researchers, and startups to design, verify, fabricate, and test their own chips and intellectual property. By prioritising design-led self-reliance, the programme lays the foundation for long-term technological competitiveness.

Backed by an outlay of ₹250 crore over five years, C2S has set ambitious and clearly defined targets. It aims to develop around 85,000 industry-ready professionals across academic levels, including 200 PhD scholars in advanced chip design research, 7,000 M.Tech graduates specialising in VLSI and embedded systems, 8,800 M.Tech graduates from allied streams with focused VLSI exposure, and nearly 69,000 B.Tech students through redesigned, VLSI-oriented coursework.

The programme is not limited to manpower creation. It also seeks tangible ecosystem outcomes such as incubating 25 startups, enabling 10 technology transfers, generating at least 50 patents, and supporting over 2,000 high-quality research publications, alongside training more than one lakh learners overall.

A defining feature of C2S is its end-to-end, hands-on training model. Participants work across the full chip design lifecycle, from architectural concepts and simulation to fabrication and silicon validation. They receive access to industry-grade Electronic Design Automation tools from leading global vendors, high-performance computing infrastructure, IP libraries, FPGA prototyping platforms, and national supercomputing resources through PARAM Utkarsh.

The ChipIN Centre, operated by Centre for Development of Advanced Computing at Bengaluru, serves as the national hub for design enablement. It offers shared infrastructure, continuous technical mentorship, design verification support, and coordinates quarterly shared wafer runs. Designs submitted by students and researchers are aggregated onto multi-project wafers and fabricated at the Semi-Conductor Laboratory using mature 180 nm technology, after which the chips are packaged and returned for testing and evaluation. This ecosystem is complemented by specialised labs such as the SMART Lab at NIELIT Calicut, which delivers short-term certification courses and additional hands-on exposure.

The scale of participation is already significant. More than 400 organisations are involved, including over 300 academic institutions and close to 100 startups, ensuring that access to tools and infrastructure is broad-based rather than limited to a few elite centres.

The programme has begun to show concrete results. Over one lakh learners have enrolled so far, with around 67,000 already trained. Six shared wafer runs have been completed, leading to 122 chip design submissions from 46 institutions and the successful fabrication and delivery of 56 student-designed chips. More than 265 industry-led training sessions have been conducted, while participating institutions have filed over 75 patents and are actively developing more than 500 IP cores, ASICs, and SoC designs for sectors such as defence, telecom, automotive, industrial systems, and consumer electronics.

Institutional coordination has been a key strength. MeitY provides policy direction, funding, and oversight, C-DAC runs the national design infrastructure through ChipIN, and SCL Mohali handles fabrication and packaging. This integrated framework promotes close academia–industry collaboration, equitable access to advanced facilities, and a steady pipeline of skilled chip designers.

Taken together, the Chips to Start-up Programme represents more than a conventional skill-development initiative. It is an ecosystem-building effort that combines training, real silicon experience, startup incubation, patent creation, and shared national infrastructure. By enabling engineers, researchers, and entrepreneurs to design and realise original chips and IP, the programme positions India to play a more substantive role in the global semiconductor landscape and strengthens its strategic autonomy in an increasingly electronics-driven world.